TOPICS

- TOPICS

- パワーエレクトロニクス実装分野の国際学会「ISAPP 2025」に採択されました。 Accepted for the international conference "ISAPP 2025".

パワーエレクトロニクス実装分野の国際学会「ISAPP 2025」に採択されました。

Accepted for the international conference "ISAPP 2025".

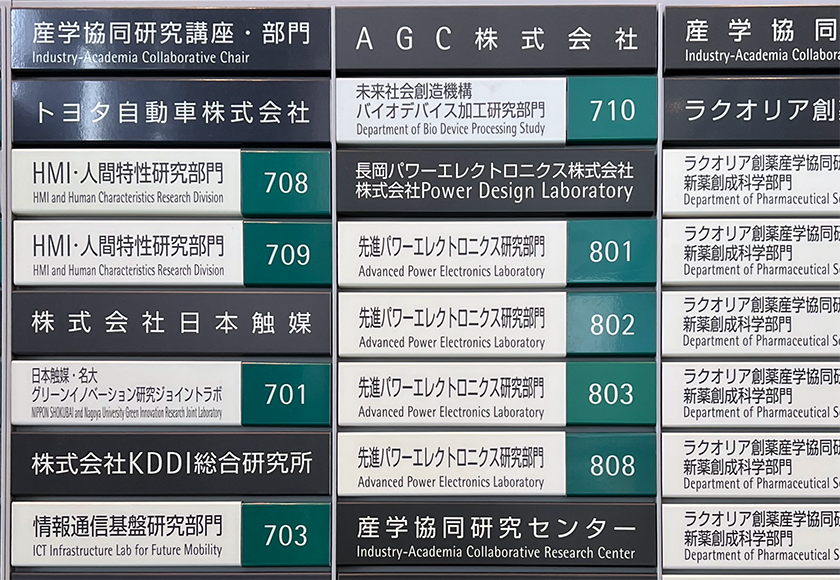

2025年11月5日~7日に福岡で開催された次世代パワーエレクトロニクスの電子材料や半導体デバイスに関わる実装技術の国際学会ISAPP 2025(International Symposium for Advanced Power Packaging 2025)にて、名古屋大学の論文が採択されました。ISAPPはSiCやGaNなどのワイドバンドギャップ半導体向けの次世代パッケージング技術に関する研究を深めるための国際的なシンポジウムで、そのエレクトロニクスへの応用について世界中の専門家や研究者が会し、自由に討論される場が提供されます。

A paper from Nagoya University has been accepted for the International Symposium for Advanced Power Packaging 2025 (ISAPP 2025), in the field of power packaging technologies for electronic materials and semiconductor devices.

The conference is an international symposium dedicated to advancing research on next-generation packaging technologies for wide bandgap semiconductors such as SiC and GaN. It provides a forum where experts and researchers from around the world gather to freely discuss their applications in electronics. ISAPP 2025 was held in Fukuoka from November 5 to 7, 2025.

“Circuit Layout Design of the Parasitic Component of the Printed Circuit Board for Multi-Parallel GaN Devices”

Wide band-gap power semiconductor devices such as SiC or GaN device are capable of high-speed switching compared to the conventionally used Si IGBTs, thus reducing switching losses and increasing the carrier frequency to improve the waveform and controllability of the motor current. The increased device mounting area causes an additional parasitic inductance and capacitance between the drain and gate of the device, which causes false turn-on and gate oscillation. This research proposes the optimal structure of a half-bridge circuit with 12 parallel power devices mounted on thick copper layer print circuit board (PCB). PCBs can suppress parasitic inductance between devices and DC link capacitors more effectively than power modules. Similarly, PCBs are effective in suppressing parasitic inductance in gate drive circuits, however, they increase the stray capacitance between the drain and gate PCB patterns. This trade-off of the distance between the gate drive circuit and the main circuit is well-controlled in this study. Then, an inverter circuit board with 12 devices mounted in parallel was constructed, and its operation was verified while suppressing false turn-on, gate oscillation, and current imbalance of devices.